# Spindle and loading motor driver for PD BA6852FP

The BA6852FP is a motor driver IC developed for use in PD, CD-ROM and DVD applications. In addition to having a conventional spindle motor driver, it includes a reversible motor driver for use with loading motors to allow easy system construction.

#### Applications

PD, CD-ROM and DVD.

#### Features

- Power save circuit (three-level switch) allows FG output in power save mode.

- FGSW allows selection between either three-phase composite output or single-phase output for the FG output.

- 3) The output voltage for the loading motor driver can be set using the Vref pin.

## ● Absolute maximum ratings (Ta = 25°C)

| Parameter                          | Symbol             | Limits          | Unit |

|------------------------------------|--------------------|-----------------|------|

| Applid voltage                     | Vcc                | 7               | ٧    |

| Applid voltage                     | V <sub>M1, 2</sub> | 15              | ٧    |

| Power dissipation                  | Pd                 | 1700*1          | mW   |

| Operating temperature              | Topr               | <b>−20~</b> +75 | °C   |

| Storage temperature                | Tstg               | <b>−55∼+150</b> | °C   |

| Junction temperature               | Tjmax              | 150             | °    |

| Output current                     |                    | 1300*2          |      |

| (spindle block)<br>(loading block) | Іомах              | 1000            | mW   |

<sup>\*1</sup> When mounted on 70mm×70mm ×1.6mm glass epoxy board. Reduced by 13.6mW for each increase in Ta of 1°C over 25°C.

#### $\bullet$ Recommended operating conditions (Ta = 25°C)

| Parameter                                                                | Symbol          | Limits  | Unit     |

|--------------------------------------------------------------------------|-----------------|---------|----------|

| Power supply voltage                                                     | Vcc             | 4.5~5.5 | ٧        |

| (spindle block motor power supply)<br>(loading block motor power supply) | V <sub>м1</sub> | 3~14    | <b>V</b> |

|                                                                          | V <sub>M2</sub> | 4.5~14  | ٧        |

<sup>\*2</sup> Should not exceed Pd or ASO values.

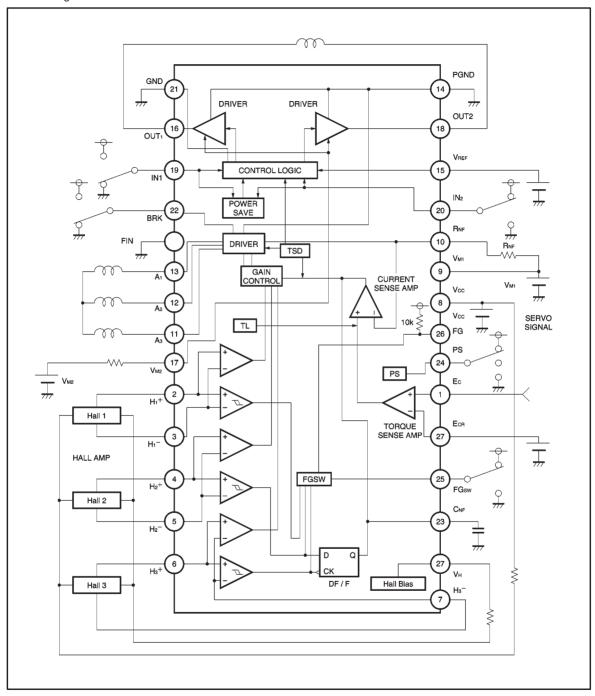

## Block diagram

# Pin descriptions

| Pin No. | Pin name         | Function                                                       |

|---------|------------------|----------------------------------------------------------------|

| 1       | Ec               | Spindle torque control                                         |

| 2       | H <sub>1</sub> + | Hall signal input pin spindle                                  |

| 3       | H1 <sup>-</sup>  | Hall signal input pin spindle                                  |

| 4       | H <sub>2</sub> + | Hall signal input pin spindle                                  |

| 5       | H <sub>2</sub> - | Hall signal input pin spindle                                  |

| 6       | H <sub>3</sub> + | Hall signal input pin spindle                                  |

| 7       | H3 <sup></sup>   | Hall signal input pin spindle                                  |

| 8       | Vcc              | Signal block power supply                                      |

| 9       | V <sub>M1</sub>  | Spindle motor power supply                                     |

| 10      | Rnf              | For connection of resistor for spindle output current detector |

| 11      | Аз               | Spindle output A3                                              |

| 12      | <b>A</b> 2       | Spindle output A2                                              |

| 13      | A <sub>1</sub>   | Spindle output A1                                              |

| 14      | PGND             | Driver GND                                                     |

| 15      | VREF             | Loading output high level voltage setting                      |

| 16      | OUT1             | Loading motor output 1                                         |

| 17      | V <sub>M2</sub>  | Loading motor power supply                                     |

| 18      | OUT2             | Loading motor output 2                                         |

| 19      | IN1              | Loading logic input                                            |

| 20      | IN2              | Loading logic input                                            |

| 21      | GND              | Signal GND                                                     |

| 22      | BRK              | Spindle brake                                                  |

| 23      | CNF              | For connection of capacitor for spindle phase compensation     |

| 24      | PS               | Spindle power save                                             |

| 25      | FGSW             | Spindle FG output switch                                       |

| 26      | FG               | Spindle FG signal output                                       |

| 27      | VH               | Hall bias                                                      |

| 28      | Ecr              | Spindle torque control reference                               |

| FIN     | FIN              | Heatsink fin                                                   |

<sup>\*</sup> The heatsink fin must be connected to GND.

•Electrical characteristics (unless otherwise noted, Ta = 25°C, Vcc = 5V, V<sub>M1</sub> = 12V, and V<sub>M2</sub> = 12V)

| Parameter                            | Symbol            | Min. | Тур. | Max. | Unit              | Coniditions                                  | Measurement<br>circuit |

|--------------------------------------|-------------------|------|------|------|-------------------|----------------------------------------------|------------------------|

| [Spindle]                            |                   |      |      |      |                   |                                              |                        |

| Circuit current 1                    | lcc1              | _    | 0.4  | 0.6  | mA                | Standby mode, I <sub>PS</sub> = $-150 \mu A$ | Fig.3                  |

| Circuit current 2                    | lcc2              | _    | 2.8  | 4.0  | mA                | Only Hall bias and FG operates               | Fig.3                  |

| Circuit current 3                    | Іссз              | _    | 5.7  | 8.0  | mA                | Operation mode, Ec=EcR                       | Fig.3                  |

| ⟨Power save⟩                         |                   |      |      |      |                   |                                              |                        |

| On current range                     | IPSON             | -350 | _    | -150 | μА                | Standby mode                                 | Fig.4                  |

| Open current range                   | IPSOP             | -15  | _    | 15   | μΑ                | Only Hall bias and FG operates               | Fig.4                  |

| Off current range                    | IPSOFF            | 150  | _    | 350  | μΑ                | Operation mode                               | Fig.4                  |

| 〈Hall bias〉                          |                   |      |      |      |                   |                                              |                        |

| Hall bias voltage                    | Vнв               | _    | 0.9  | 1.5  | V                 | I <sub>HB</sub> =10mA                        | Fig.5                  |

| 〈Hall amplifier〉                     |                   |      |      |      |                   |                                              |                        |

| Input bias current                   | Іна               | _    | 0.7  | 2.0  | μΑ                | _                                            | Fig.6                  |

| Same-phase input voltage range       | VHAR              | 1.5  | _    | 4.0  | V                 | _                                            | Fig.6                  |

| Minimum input level                  | VINH              | 50   | _    | _    | mV <sub>P-P</sub> | _                                            | Fig.6                  |

| Hall hysteresis                      | V <sub>H</sub> ys | 5    | 20   | 40   | mV                | _                                            | Fig.12                 |

| ⟨Torque command⟩                     |                   |      |      |      |                   |                                              |                        |

| Input voltage range                  | Ec, Ecr           | 1.0  | _    | 4.0  | V                 | _                                            | Fig.7                  |

| Offset+                              | Ecof +            | 20   | 50   | 80   | mV                | With respect to Ec=2.5V                      | Fig.7                  |

| Offset-                              | Ecof —            | -80  | -50  | -20  | mV                | _                                            | Fig.7                  |

| Input bias current                   | Ecin              | -3   | -0.4 | 3    | μΑ                | Ec=2V, EcR=2.5V                              | Fig.7                  |

| I / O gain                           | GEC               | 0.4  | 0.5  | 0.6  | A/V               | Ec=1.5, 2.0V                                 | Fig.7                  |

| ⟨Brake⟩                              |                   |      |      |      |                   |                                              |                        |

| On voltage range                     | Vsbon             | 3.5  | _    | _    | V                 | Brake on mode                                | Fig.8                  |

| Off voltage range                    | Vsboff            | _    | _    | 1.5  | V                 | Brake off mode                               | Fig.8                  |

| ⟨FG⟩                                 |                   |      |      |      |                   |                                              |                        |

| FGSW input low level voltage         | VswL              | _    | _    | 1.5  | V                 | FG1 phase output                             | Fig.9                  |

| FGSW input high level voltage        | Vswн              | 3.5  | _    | _    | V                 | FG3 phase composition output                 | Fig.9                  |

| FG output high level voltage         | VFGH              | 4.5  | 4.9  | 5.0  | V                 | I <sub>FG</sub> =-10 μ A                     | Fig.10                 |

| FG output low level voltage          | VFGL              | 0    | 0.2  | 0.35 | V                 | I <sub>FG</sub> =5.0mA                       | Fig.10                 |

| Duty (reference value)               | Du                | _    | 50   | _    | %                 | _                                            | _                      |

| ⟨Output⟩                             |                   |      |      |      |                   |                                              |                        |

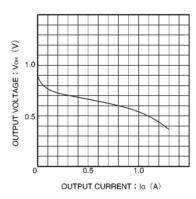

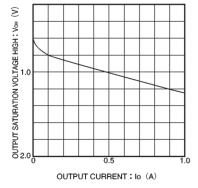

| Output saturation high level voltage | Vон               | _    | 1.0  | 1.5  | V                 | lo=-600mA                                    | Fig.11                 |

| Output saturation low level voltage  | Vol               | _    | 0.4  | 0.9  | V                 | lo=600mA                                     | Fig.11                 |

| Vм drive current                     | IVMD              | _    | 50   | 85   | mA                | Ec=0V<br>Output open                         | Fig.12                 |

| Output limit current                 | lτι               | 560  | 700  | 840  | mA                | R <sub>NF</sub> =0.5Ω                        | Fig.5                  |

$\bigcirc$ Not designed for radiation resistance.

| Parameter                  | Symbol | Min. | Тур. | Max.                 | Unit | Coniditions             | Measurement<br>circuit |

|----------------------------|--------|------|------|----------------------|------|-------------------------|------------------------|

| [Loading block]            |        |      |      |                      |      |                         |                        |

| Circuit current 4          | Icc4   | 12   | 24   | 36                   | mA   | Forward or reverse mode | Fig.13                 |

| Circuit current 5          | lcc5   | 29   | 48   | 67                   | mA   | IN1="H", IN2="H"        | Fig.13                 |

| Input voltage high level   | Vıн    | 2.1  | _    | _                    | V    | _                       | Fig.13                 |

| Input voltage low level    | VIL    | _    | _    | 0.8                  | V    | _                       | Fig.13                 |

| High level input voltage   | lін    | 45   | 90   | 135                  | μΑ   | V <sub>IN</sub> =2V     | Fig.13                 |

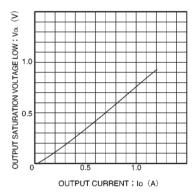

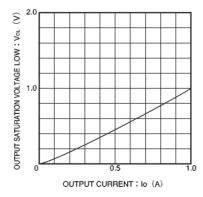

| Outout saturation voltage* | Vce    | _    | 1.0  | 1.5                  | V    | Io=0.2A                 | Fig.14                 |

| VREF pin outflow current   | IREF   | _    | 2.0  | 5.0                  | μΑ   | Io=0.1A, VREF=9V        | Fig.15                 |

| VREF input voltage range   | VREF   | _    | _    | (V <sub>M2</sub> )-1 | V    | _                       | Fig.15                 |

$<sup>\</sup>ensuremath{\boldsymbol{\ast}}$  The output saturation voltage is the sum of the upper and lower output Tr.

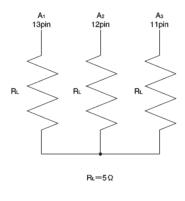

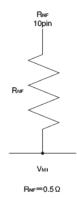

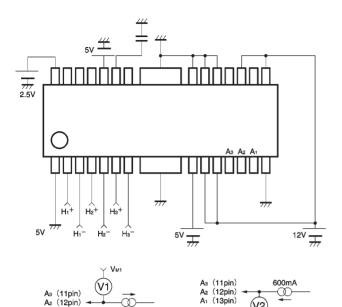

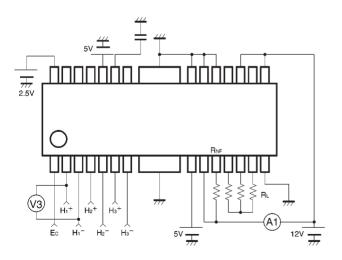

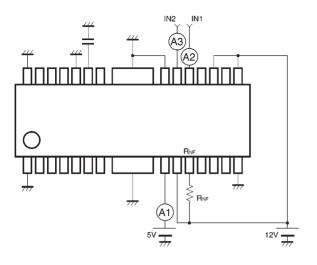

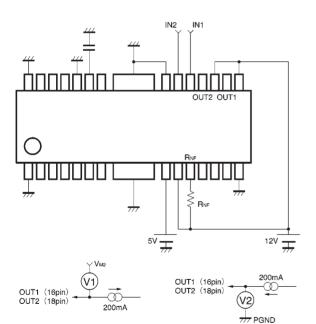

## Measurement circuits

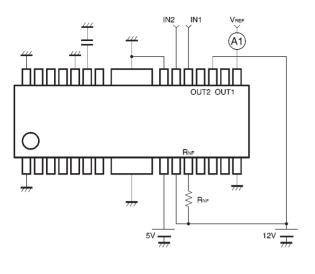

## (1) Measurement circuit resistance

Fig.2

# (2) Input/output table

|             | Input conditions |                  |                  |                 |                  |     | Output state    |            |    |            |            |    |                   |

|-------------|------------------|------------------|------------------|-----------------|------------------|-----|-----------------|------------|----|------------|------------|----|-------------------|

|             |                  | Input conditions |                  |                 |                  |     | Forward Reverse |            |    | €          | NA         |    |                   |

| Pin No.     | 2                | 3                | 4                | 5               | 6                | 7   | 13              | 12         | 11 | 13         | 12         | 11 | Measurement point |

| Pin Name    | H₁+              | H <sub>1</sub> - | H <sub>2</sub> + | H2 <sup>-</sup> | H <sub>3</sub> + | Нз- | <b>A</b> 1      | <b>A</b> 2 | Аз | <b>A</b> 1 | <b>A</b> 2 | Аз |                   |

| Condition 1 | L                | М                | Н                | М               | М                | М   | Н               | L          | L  | L          | Н          | Н  | 13pin HIGH        |

| Condition 2 | Н                | М                | L                | М               | М                | М   | L               | Н          | Н  | Н          | L          | L  | 13pin LOW         |

| Condition 3 | М                | М                | L                | М               | Н                | М   | L               | Н          | L  | Н          | L          | Н  | 12pin HIGH        |

| Condition 4 | М                | М                | Н                | М               | L                | М   | Н               | L          | Н  | L          | Н          | L  | 12pin LOW         |

| Condition 5 | Н                | М                | М                | М               | L                | М   | L               | L          | Н  | Н          | Н          | L  | 11pin HIGH        |

| Condition 6 | L                | М                | М                | М               | Н                | М   | Н               | Н          | L  | L          | L          | Н  | 11pin LOW         |

Note: Forward Ec < Ecr Reverse Ec > Ecr Input voltage

H = 2.6V

M = 2.5V

L = 2.4V

ONot designed for radiation resistance.

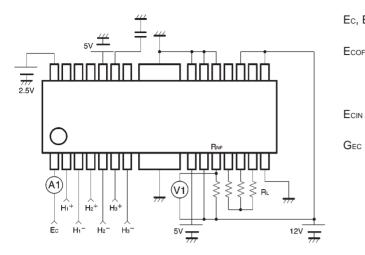

### (3) Measurement circuits

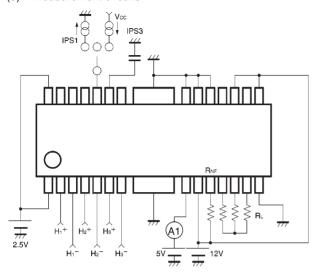

Fig.3

lcc1 : Ammeter A1 value IPS1 = 150 $\mu$ A H<sub>1</sub><sup>-</sup>, H<sub>2</sub><sup>-</sup>, H<sub>3</sub><sup>-</sup> = Vcc / 2 (V)

$H_1^+, H_2^+, H_3^+ = V_{CC} / 2 + 0.1 \text{ (V)}$   $I_{CC2}$ : Ammeter A1 value

PS = OPEN  $H_1^-$ ,  $H_2^-$ ,  $H_3^-$  = Vcc / 2 (V)  $H_1^+$ ,  $H_2^+$ ,  $H_3^+$  = Vcc / 2 + 0.1 (V)

lcc3 : Ammeter A1 value  $IPS3 = 150 \mu A \\ H_1^-, H_2^-, H_3^- = Vcc / 2 \text{ (V)} \\ H_1^+, H_2^+, H_3^+ = Vcc / 2 + 0.1 \text{ (V)}$

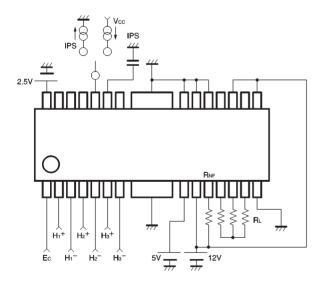

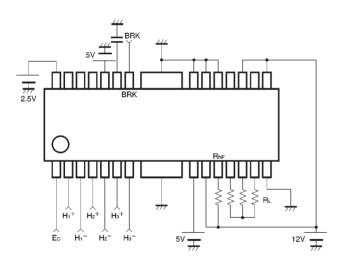

Fig.4

IPSON : IPS range for which all output pins

are open

(input conditions 1 to 6)

$\ensuremath{\mathsf{IPSOP}}\xspace$  : IPS range for only FG and the hall

bias operate

(input conditions 1 to 6)

IPSOFF: PS range for which the output pins

are as in the Input / output table

(input conditions 1 to 6)

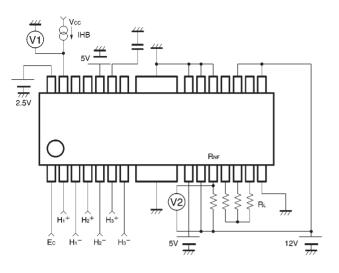

Fig.5

Vнв : Voltmeter V1value VPS = 5VIHB = 10mA

: (Voltmeter V2value) / 0.5 ITL

> VPS = 5VEc = 0V

(input conditions 1 to 6)

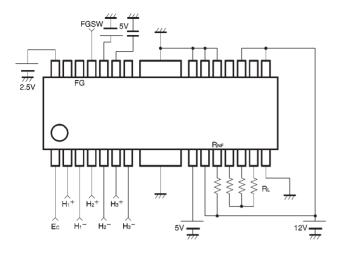

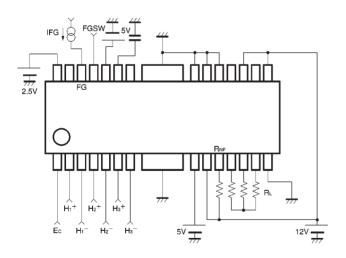

Fig.6

: With  $Hn^{+} = 4.0V$ .  $Hn^{-} = 2.5V$ . Іна the current that flows into Hn+ With  $Hn^{+} = 2.5V$ .  $Hn^{-} = 4.0V$ . the current that flows into Hn-

(n = 1, 2, 3)

VHAR : Hall input voltage range for which the output pin is as per the Input / output table.

VINH : Hall input level for which the output pin is as per the Input / output table.  $|Hn^+ - Hn^-|$

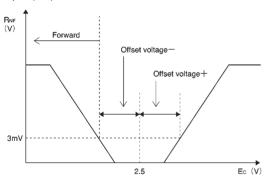

Fig.7

Ec, Ecr : Torque command operation

voltage range

Ecof±: Vary Ec until Ecr = 2.5V, then

Vary Ec voltmeter V1 < 3mV.

This Ec voltage range

(see operation notes (2)).

: Ammeter value when

$E_C = 2V$  and  $E_{CR} = 2.5V$  $G_{EC}$ : If the V1 value is V2 when

$E_c = 1.5V$ , and the V1 value is V3 when  $E_c = 2.0V$  $G_{EC} = \{(V2 - V3) / (2.0 - 1.5)\}/$

RNF (RNF =  $0.5\Omega$ )

Fig.8

Vsbon : BRK pin voltage range when all

output pins are low.

VSBOFF : BRK pin voltage range when all

output pins are as per the Input /

output table.

Fig.9

VswL : FGSW pin voltage range when the hall input and FG output are as per the table below.

| H <sub>1</sub> + | H <sub>2</sub> + | H <sub>3</sub> + | FG |  |  |  |  |

|------------------|------------------|------------------|----|--|--|--|--|

| L                | Н                | Н                | L  |  |  |  |  |

| Н                | L                | L                | Н  |  |  |  |  |

| H=2.6V           | H=2.6V, L=2.4V   |                  |    |  |  |  |  |

V<sub>SWH</sub>: FGSW pin voltage range when the hall input and FG output are as per the table below.

| H₁+ | H <sub>2</sub> + | <b>Н</b> з <sup>+</sup> | FG |

|-----|------------------|-------------------------|----|

| L   | L                | н                       | L  |

| Н   | L                | Н                       | Н  |

| Н   | L                | L                       | L  |

| Н   | Н                | L                       | Н  |

| L   | Н                | L                       | L  |

| L   | Н                | Н                       | Н  |

H=2.6V, L=2.4V

Hn<sup>-</sup>=2.5V

Fig.10

V<sub>FGH</sub>: Voltmeter V1 value

(Input / output table, condition 2)

$IFG = -10\mu A$  FGSW = 0V

V<sub>FGL</sub>: Voltmeter V1 value

(Input / output table, condition 1)

IFG = 3mAFGSW = 0V

PGND

Fig.11

600mA

A<sub>1</sub> (13pin)

VoH : With the output measurement pin made high level according to the input conditions, the V1 value when 600mA flows from that pin.

Vol : With the output measurement pin made low level according to the input conditions, the V2 value when 600mA flows from that pin.

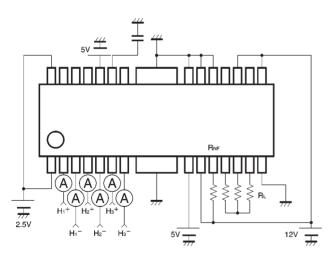

Fig.12

$V_{\text{HYS}}\,$  : The voltage difference V3 between  ${H_1}^+$  and  ${H_1}^-$  that switch the FG pin.

Ec = 2.5VFGSW = 0V

IVMD : Ammeter A1value

Output open (input conditions 1 to 6)

Ec = 0V

Fig.13

Fig.14

$I_{CC4}$ : Ammeter A1 value IN1 = 5V, IN2 = 0V

Iccs : Ammeter A1 value IN1 = 5V, IN2 = 5V

V<sub>IH</sub> : IN1 range for which OUT1 = High, OUT2 = Low (IN2 = Low)

> IN2 range for which OUT1 = Low, OUT2 = High (IN1 = Low)

V<sub>IL</sub>: IN1 range for which OUT1 = Low,

OUT2 = High (IN2 = High)

IN2 range for which OUT1 = High,

OUT2 = Low (IN1 = High)

I<sub>IH</sub>: Ammeter A2 value when IN1 = 2V Ammeter A3 value when IN2 = 2V

Vce : Sum of V1 (the value when 200mA is flowing from the output high level pin) and V2 (the value when 200mA is flowing to the output low level pin).

OUT1 (16pin) OUT2 (18pin) 100mA

Fig.15

## Operation notes

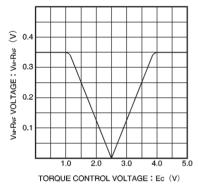

## (1) Torque command

The  $R_{NF}$  pin voltage with respect to the torque command input (EC) is as follows.

Fig.16

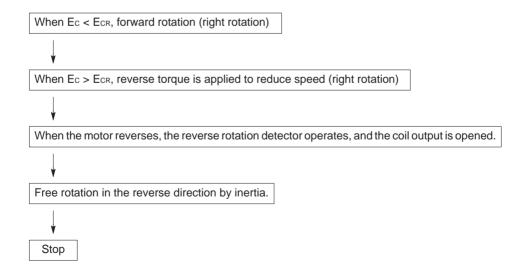

|                                        | Rotation direction |

|----------------------------------------|--------------------|

| Ec <ecr< td=""><td>Forward</td></ecr<> | Forward            |

| Ec>EcR                                 | Reverse*           |

<sup>\*</sup> Stops after reverse is detected.

$I_{REF}$ : Ammeter A1 value  $I_0 = 100 mA$   $V_{REF} = 9V$

VREF : VREF pin voltage range for which the output voltage can be controlled

The I / O gain GEC from the Ec pin to the RNF (output current) is determined by the RNF detector resistance.

$$G_{EC} = 0.25 / R_{NF} (A / V)$$

The torque limit current I<sub>T</sub>∟ is given by

$$I_{TL} = 0.35 / R_{NF} (A)$$

.

#### (2) Power save

The power save pin logic is as follows.

| Mode                         | PS pin                        |

|------------------------------|-------------------------------|

| Power save mode              | Outflow or pulled down to GND |

| FG, hall bias operation mode | Open                          |

| Spindle operation mode       | Inflow or pulled up to Vcc    |

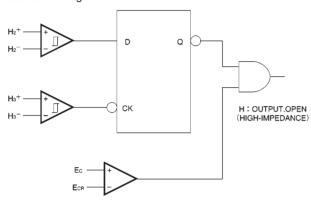

#### (3) Reverse rotation detector

The construction of the reverse rotation detector circuit is shown in Fig. 17.

Fig.17

## 1) Forward (Ec < Ecr)

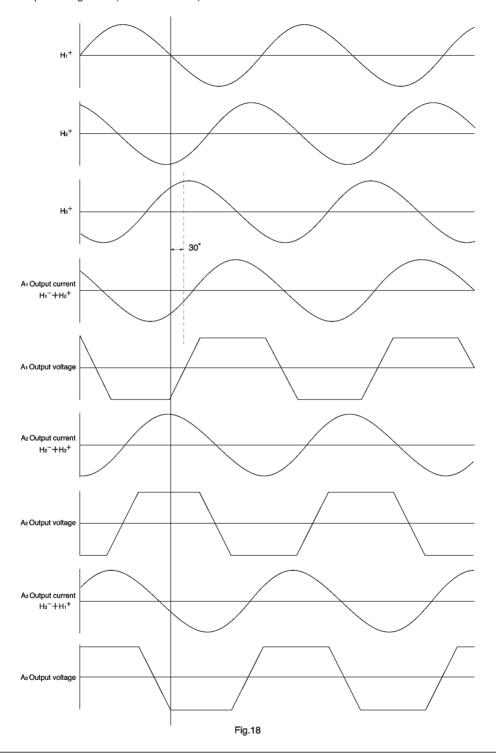

The phase relationship between the hall input signals  ${\rm H_2}^+$  and  ${\rm H_3}^+$  is as shown in Fig.18, and the reverse rotation detector circuit does not operate.

## 2) Reverse (Ec > Ecr)

The phase relationship between  $\rm H_2^+$  and  $\rm H_3^+$  is opposite to that for forward rotation, and the reverse rotation detector circuit operates to switch the output off and leave it in the open state.

Motor operation during reverse detection

(4) Input / output timing chart (forward rotation)

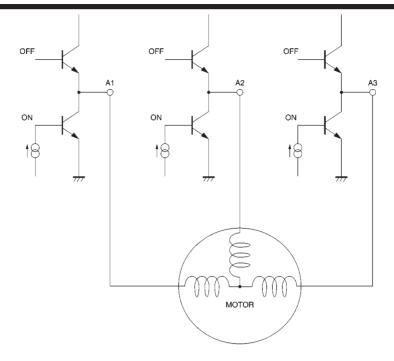

## (5) Short brake

Fig.19

When the BRK pin goes to high level, the upper-side output transistors (three phase) go off, and the lower-side output transistors (three phase) go on.

## (6) Hall input

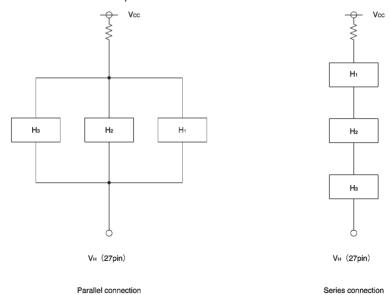

The hall pins can be connected in series or parallel.

Fig.20

#### (7) FG output switch

The relationship between the FG output switch pin and the FG output is as follows.

|          | FG output mode               |

|----------|------------------------------|

| FGSW="H" | Three-phase composite output |

| FGSW="L" | Single-phase output          |

## (8) About the input pin applied voltage

Do not apply voltage to any of the other pins when the  $V_{\rm CC}$  voltage is not being supplied to the IC. In addition, when  $V_{\rm CC}$  is being applied, do not apply a voltage more than  $V_{\rm CC}$  to any of the other pins.

#### (9) Input pins

The loading input pin has a negative temperature characteristic, so when using it, give due consideration to the temperature characteristics.

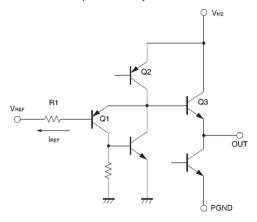

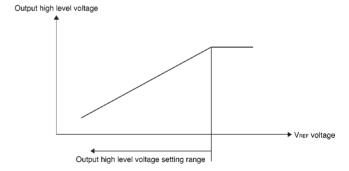

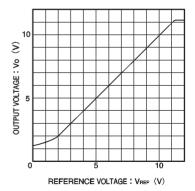

## (10) VREF pin (output high level voltage setting)

The loading block output high level voltage can be set using the  $V_{\text{REF}}$  pin voltage.

The output high level voltage  $V_{\text{OH}}$  is given by the following formula.

$$V_{OH} = V_{REF} + I_{REF} \times R1 + VBE (Q1) - VBE (Q3)$$

The  $V_{REF}$  voltage that brings about the above formula is up to  $V_{M2}$  –  $V_{CE}$  (Q2) – VBE (Q3).

Do not apply a voltage of more than  $V_{M2}$  to the  $V_{REF}$  pin. Short the  $V_{REF}$  pin to  $V_{M2}$  if you will not use it.

Fig.21

Fig.22

## (11) Spindle and loading operation conditions

When IN1 or IN2 are high level, the spindle is off regardless of the PS pin input.

| PS | Spindle operation mode                   | IN1 | IN2 | OUT1 | OUT2 |

|----|------------------------------------------|-----|-----|------|------|

| *  | Refer to item (2) of the operation notes | L   | L   | OPEN | OPEN |

| ** | OPEN                                     | Н   | L   | Н    | L    |

| ** | OPEN                                     | L   | Н   | L    | Н    |

| ** | OPEN                                     | Н   | Н   | L    | L    |

\* : Refer to item of (2) the operation notes.

\*\* : All input patterns.

#### (12) Driver section ground (GND)

PGND (pin 14) is the driver section GND, and is not connected to the signal section GND. This is the motor current path, so take care with the PCB track width and arrangement on the PC board.

#### (13) Thermal shutdown (TSD)

When the junction temperature reaches 175°C (Typ.), the motor output is opened. There is approximately 15°C (Typ.) of temperature hysteresis.

#### Electrical characteristics curves

Fig.23 Torque gain / limit characteristics

Fig.24 Spindle upper-side output saturation characteristics

Fig.25 Spindle lower-side output saturation characteristics

Fig.26 Loading section upper-side output saturation characteristics

Fig.27 Loading section lower-side output saturation characteristics

Fig.28 VREF Vout characteristics

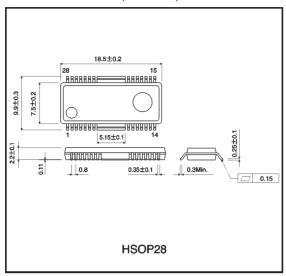

# ●External dimensions (Units: mm)